The Viterbi core implements a convolutional Viterbi decoder suitable for IEEE 802.11 a/g and Hiperlan/2. It can be implemented using a Register Exchange (RE) structure or a Trace-Back (TB) structure, depends on the area and latency requirements. Its more important features and an a performance examples are shown below.

Viterbi core features:

- Fixed code rate of 1/2

- Constraint length K from 4 to 9

- Hard and quantized Soft decision Decoding

- Parameterizable options for soft data input from 2 to 10 bits

- Register Exchange and Trace-back method for survivor memory

- Variable traceback length up to 160

- Best state logic traceback

- Fully synchronous 1x or 2x versions

Implementation example

The Viterbi core was implemented in a Virtex-5 device (speed grade -3) with the following features:

- Code rate = 1/2

- Constraint length K = 7

- 6 bits Soft decision decoding

- Taceback length D = 63

- Register Exchange and Trace-Back method

- Fully synchronous 1x version

The following table shows the area, maximum data rate, latency and power consumption achieved by this core:

|

|

Register Exchange

|

Trace-Back

|

|---|---|---|

|

Area [slices]

|

4113 Slices

|

2178 Slices

|

|

Area [BSRAMs]

|

0 BSRAMs

|

2 BSRAMs

|

|

Max. Data Rate

|

310 Mbps

|

320 Mbps

|

|

Latency

|

72 Clock cycles

|

199 Clock cycles

|

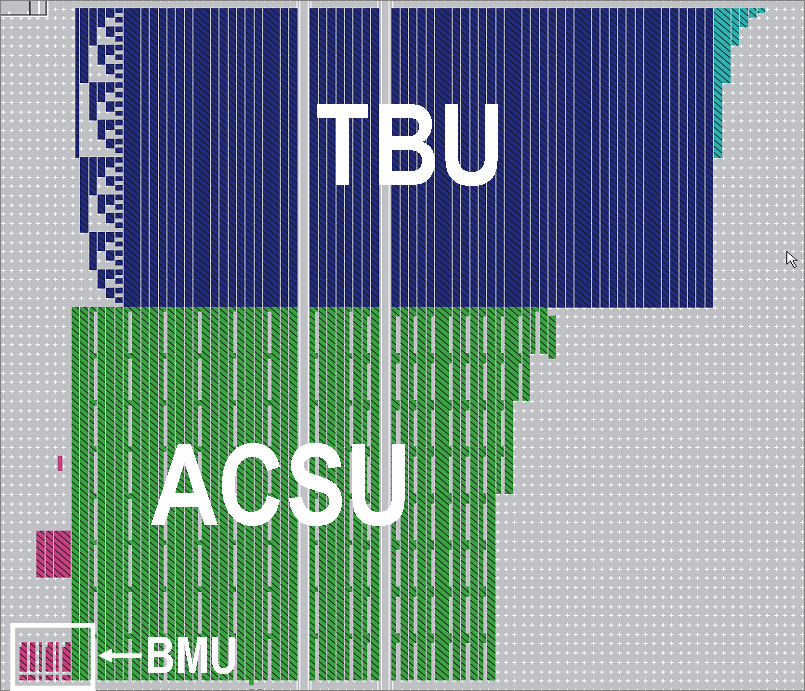

The next figure shows the layout for the previous Viterbi implementation using Register Exchange method