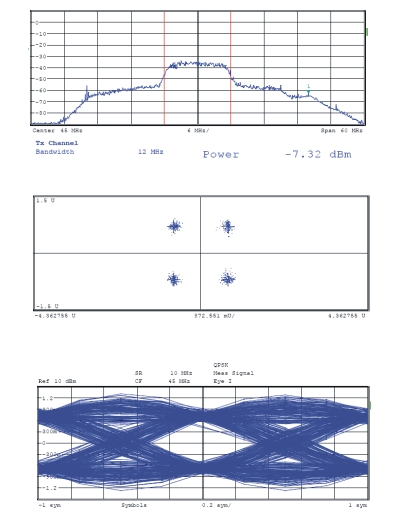

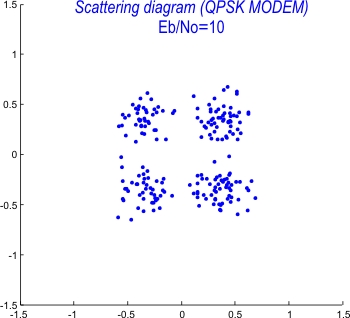

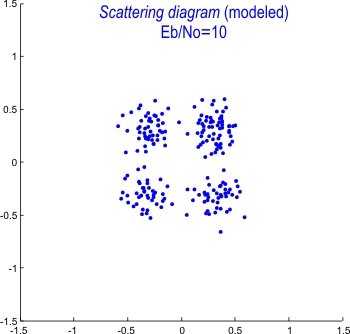

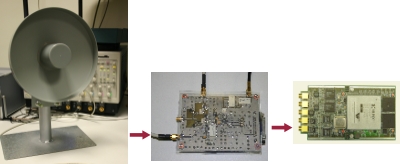

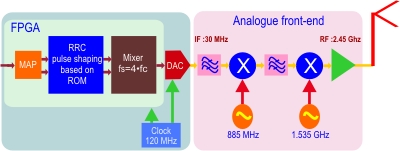

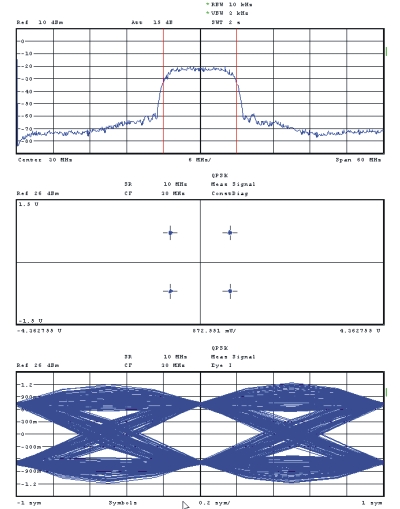

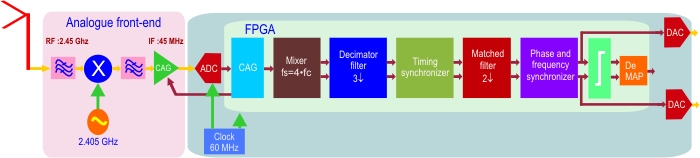

This hardware demonstrator of a QPSK MODEM transmits a symbol rate of 10 MSPS in the band of 2.4 GHz. The QPSK signal is generated by the FPGA at an intermediate frequency of 30 MHz. This signal is mixed up to 2.4 GHz by the analogue front-end. In the receiver side, the 2.4 GHz signal is translated to an intermediate frequency of 45 MHz. The signal is sub-sampling and down-converted to base-band and demodulated by the FPGA device.

- Symbol rate: 10 MSPS

- Pulse shaping: Root Raised Cosine (RRC) with a roll-off factor of 0.34 and a delay of 4, implemented with a ROM that directly generates an interpolated by a factor of 12 signal

- Intermediate frequency digitally generated at 30 MHz in transmission (sample frequency 120 MHz)

- Simplified mixer: fs = 4·fc

- Intermediate frequency at 45 MHz in reception sub-sampled at 60 MHz: generates an digital intermediate frequency of fs/4 (15 MHz)

- Simplified mixer: fs=4fc

- Decimator filter by a factor of 3

- Timing synchronize: feedback loop working at 2 samples/symbol

- Gardner timing error detector

- Fractional Lagrange interpolator by 16

- Decimator by 2 matched filter

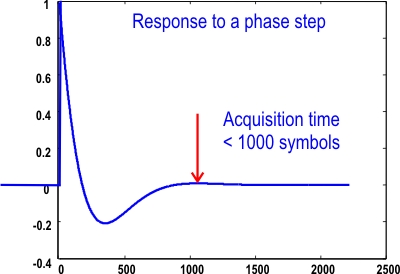

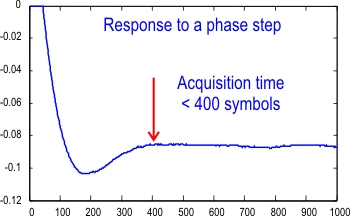

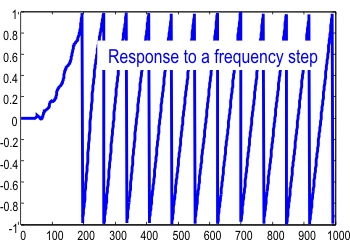

- Phase and frequency synchronize: feedback loop working at 1 sample/symbol

- Costas detector

QPSK receiver scheme